Modifikasi rangkaian Darlington LANEY CD650 adalah langkah modifikasi komponen dan transistor pada Power Amplifier buatan LANEY buatan era 90-an lalu.

CD650 adalah sebauh Power Amplifier dengan Mixer Audio 6 kanal di dalamnya yang menghasilkan keluaran hingga 500 Watt beban 4 Ohm.

Table of Contents

Penampakan seperti gambar ini:

Setiap kanal input memiliki Preamp mic tersendiri. Input Mic tersedia dalam bentuk soket XLR untuk Mic Balance dan Soket Akai untuk input LINE.

Setiap Preamp Mic ini memiliki potensio yang bertugas sebagai pengatur Level, Monitor, Effect dan 3 potensio Tone Control.

Ada pula Fitur Effek Digital 12 preset yang dapat kita pilih. Antara lain adalah Delay 1 hingga Delay 4, Concert, Arena, Club, Chamber, Garage, Bright, Dark, dan Spring.

Equalizer master 7 kanal tersedia untuk Jalur MAIN dan jalur MONITOR.

INFORMASI AWAL

Untuk mendapatkan informasi bahan modifikasi, maka saya harus mendaapatkan informasi dari rangkaian Power Amplifier ini.

Informasi yang harus kita dapatkan adalah schematic Diagram aslinya, melakukan gambar ulang dan meneliti kesesuaian rangkaian.

Jika telah benar rangkaian yang telah tergambar ulang ini maka kita sudah bisa melakukan modifikasi.

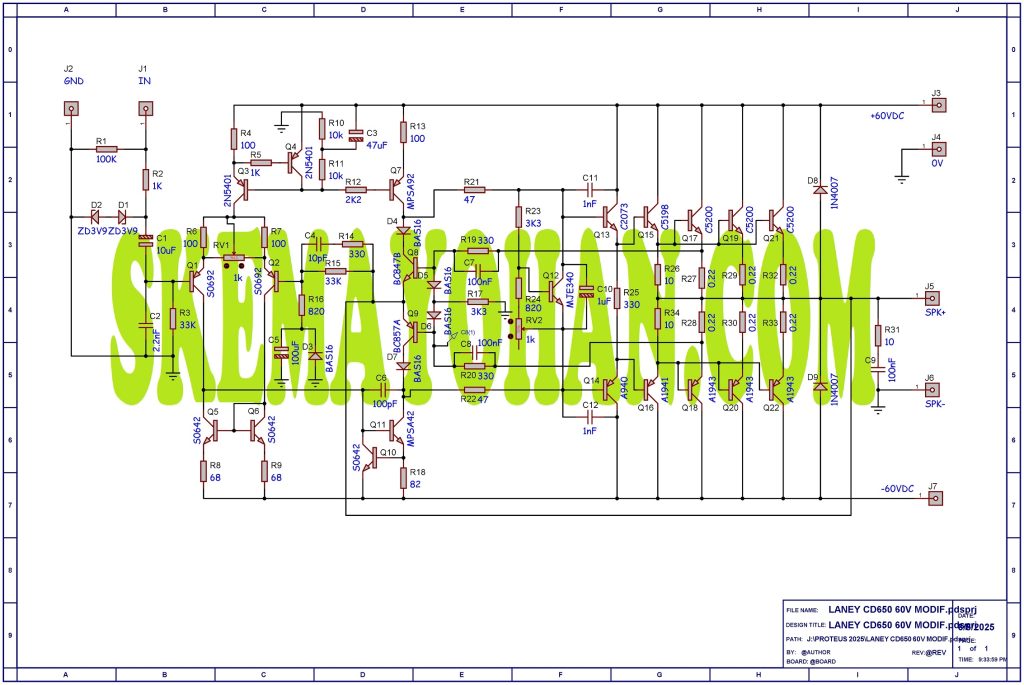

SCHEMATIC DIAGRAM

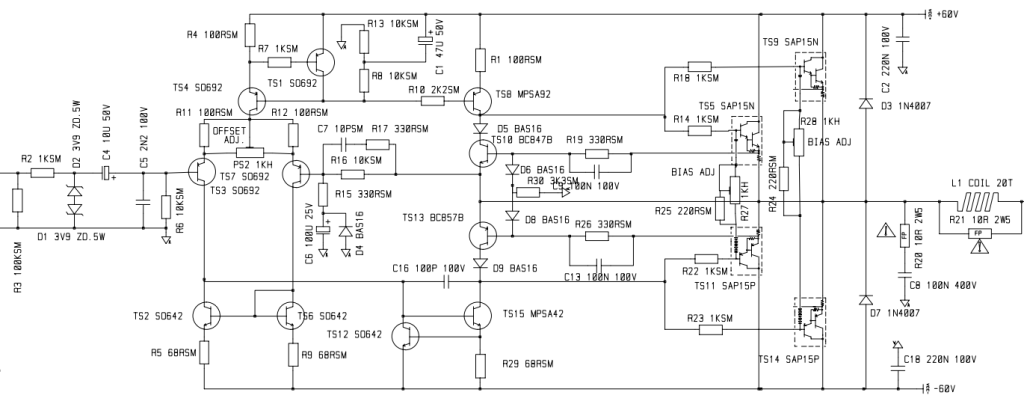

Berikut ini adalah schematic Diagram awal dari :LANEY seri CD650.

Tegangan Supply untuk Power Amplifier ini ada pada 60VDC. Dengan tegangan sebesar ini maka akan memungkinkan bagi rangkaian ini untuk mencapai angka 324W.

Namun LANEY sendiri hanya mematok angka 250W untuk masing-masing kanalnya pada beban 4 Ohm.

Saya rasa ini ada benarnya karena dengan memperhatikan transistor Final yang sebanyak 2 set masing-masing adalah 150W_dc, maka akan ketemu angka 300W_dc untuk masing-masing kanal.

Dengan mematok angka 250W tiap kanal pada beban 4 Ohm, makan tegangan ke terminal speaker adalah sekitar 32V_rms.

Jika sinyal input maksimum adalah 1rms, maka GAIN untuk rangkaian ini adalah sekitar 32X.

Rangkaian Power amplifier ini melibatkan banyak komponen transistor pada tiap bloknya.

Apabila pada skema umum adalah perlu sekitar 5 transistor untuk Preamp hingga Driver Amplifier, maka rangkaian ini memerlukan sekitar 11 transistor.

Ini dikarenakan pada tiap-tiap blok memiliki fitur Limiter.

Disamping ada fitur tambahan lainnya seperti Cermin arus dan OCP (Over Current Protection).

SPEK KOMPONEN

Transistor yang terpasang pada rangkaian Power Amplfieir ini menggunakan nomer yang tidak begitu terkenal di negeri kita.

Karena itu pada skema akhir rangkaian ini saya telah melakukan pengubahan nomer transistor yang mengikuti kearifan lokal negeri kita.

Nomer , Type, Pdc, Vce_Max, Ic_Max, hfe, File

- S0692, PNP,

- S0642, NPN,

- MPSA92, PNP,

- MPSA42, NPN,

- BC847B, NPN,

- BC857B, PNP,

- SAP15N, NPN

- SAP15P, PNP,

BC847B dan BC857B adalah transistor berbentuk SMD. Ini sulit untuk kita dapatkan.

SIMULASI PENGUKURAN TEGANGAN DC

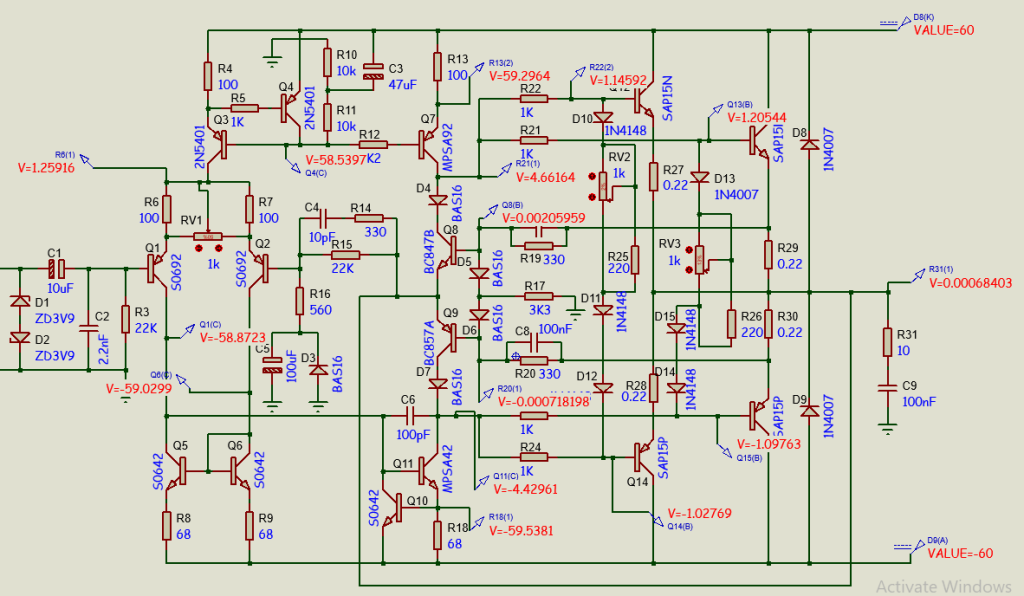

Ketika kita akan memutuskan rangkaian ini akan coba kita kloning, maka kita harus lakukan gambar ulang terlebih dahulu dan kita tes rangkaiannya untuk memastikan apakah gambar yang telah kita buat ini telah sesuai.

Tes yang dilakukan adalah Tes dengan memberi tegangan DC pada rangkaian serta memberi sinyal sinus pada titik input untuk memastikan bahwa Output rangkaian Power ini menghasilkan tegangan yang sesuai dengan patokan Amplifier.

Berikut ini adalah hasil pengukuran pada berbagai titik rangkaian pada saat ada tegangan Supply sebesar 60VDC simetris.

Tegangan pada terminal output ke speaker adalah sudah benar 0,6mV.

Voltase pada pin Basis transistor Darlington SAP15N/P ini sudah benar sekitar 1,0 hingga 1,2V.

Selanjutnya pada basis transistor OCP Q8 dan Q9 telah benar tidak boleh lebih dari 200mV.

Arus yang melalui transistor VAS(+) Q7 adalah sebesar (60-59,2)/R13= 0,8/100 = 8mA.

Sementara itu arus yang melewati VAS (-) Q11 adalah sekitar (-59,5 – -60)/R18 = 0,5/68 = 7,3mA.

Dengan demikian dissipasi daya pada transistor Q7 dan Q11 adalah sebesar (59,3-4,6)*8= 437mW dan ((-)4,4- (-)59,5)* 7,3= 402mW.

Sementara itu Dissipasi daya untuk transistor Q1 hingga Q6 tidak saya hitung karena angka yang lebih kecil dari 200mW pada 60V.

SIMULASI PENGUKURAN SINYAL SINUS

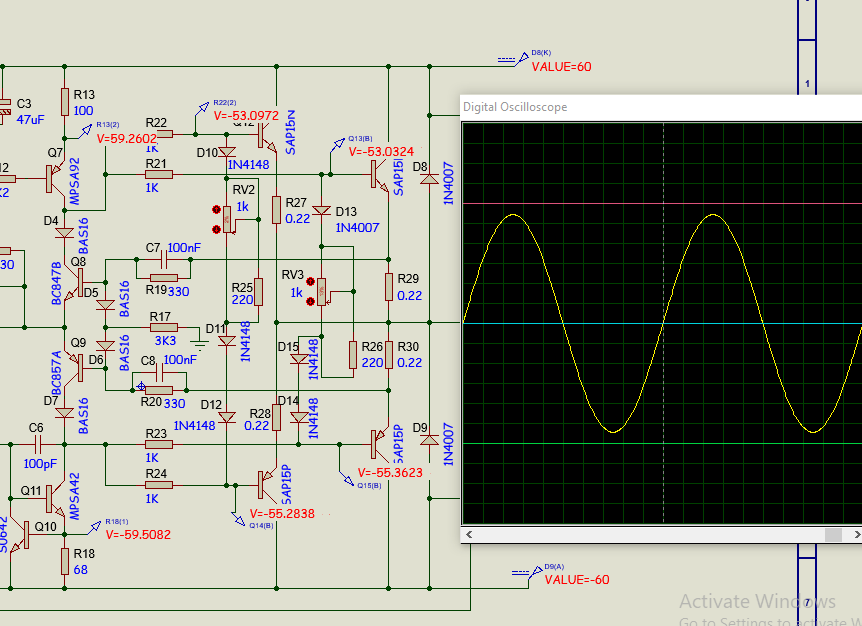

Setelah selesai memastikan tegangan DC pada berbagai titik adalah sesuai, maka kita lakukan simulasi rangkaian dengan jalan memberikan sinyal sinus pada titik input untuk selanjutnya kita baca effek amplifikasinya pada titik output.

Berikut adalah hasil simulasi sinyal sinus untuk rangkaian Power LANEY ini.

Output mendekati tegangan supply dan saya anggap ini sudah sesuai.

MODIFIKASI RANGKAIAN DARLINGTON LANEY CD650 MENJADI TR FINAL GENERIC

Modifikasi kita lakukan karena saya memperhatikan bahwa transistor Final dari rangkaian ini lumayan sulit untuk mendapatkannya.

Sekalipun ada , harganya lumayan mahal.

Ka’rena itu saya mencoba mensimulasi rangkaian ini dengan menggantikan dengan transistor nomer lain.

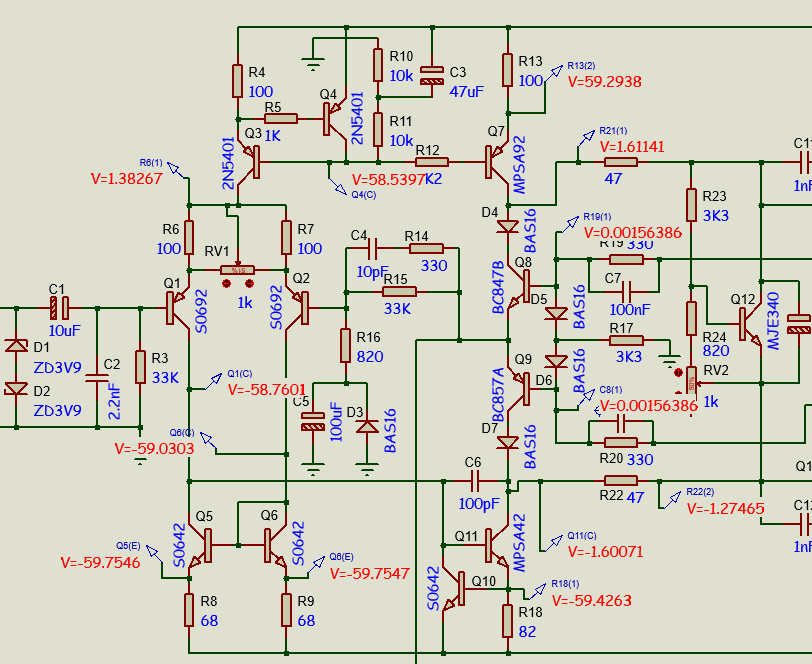

Berikut ini adalah nilai tegangan Dc pada titik-titik penting rangkaian ini pada saat ada sinyal masuk sebesar 1Vrms frekwensi 1kHz.

Nampaknya tidak ada peruahan yang signifikan pada rangkaian ini ketika ada sinyal input masuk ke rangkaian ini.

Namun akan berbeda ketika kita mengukur arus yang bekerja pada rangkaian ini terlebih apabila menggunakan beban sebesar 4 Ohm.

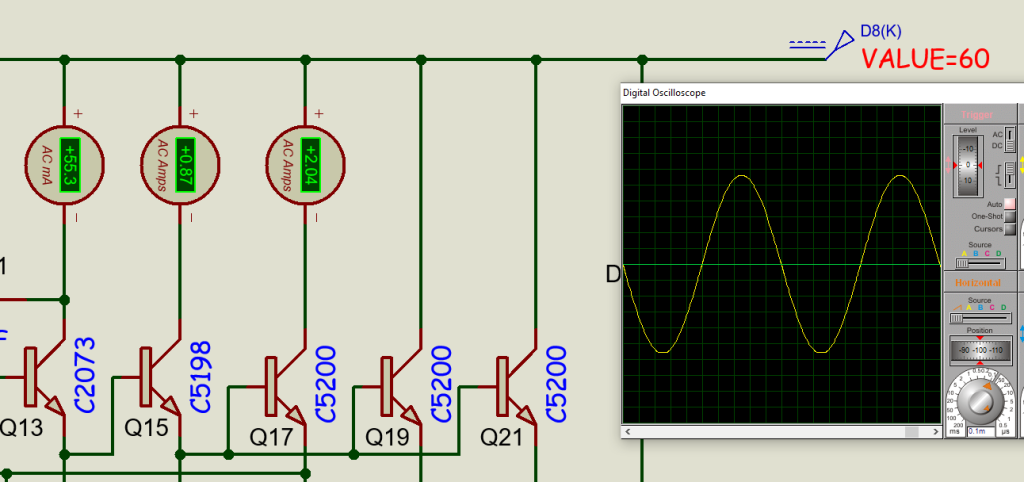

Perhatikan gambar berikut:

Transistor Driver pertama mengambil arus sebesar 55mA_rms yang berarti ada dissipasi daya hingga (60X55mA)=3,3W_rms.

Transistor Driver kedua mengambil arus sebesar 0.87A_rms yang berarti ada dissipasi daya sebesar ( 0,87x 60V ) = 52,2W_rms.

Sedangkan untuk transistor Final mengalirkan arus masing-masing sebesar 2,04A_rms pada tegangan kerja 60V yang berarti akan ada dissipasi daya hingga 122W_rms.

SCHEMATIC DIAGRAM FINAL

Selanjutnya di bawah ini adalah schematic diagram hasil modifikasi untuk menggantikan transistor Final berjenis darlington ke transistor generik dengan gaya TEF.

Schematic LANEY pada blog saya yang lain LIHAT SINI.